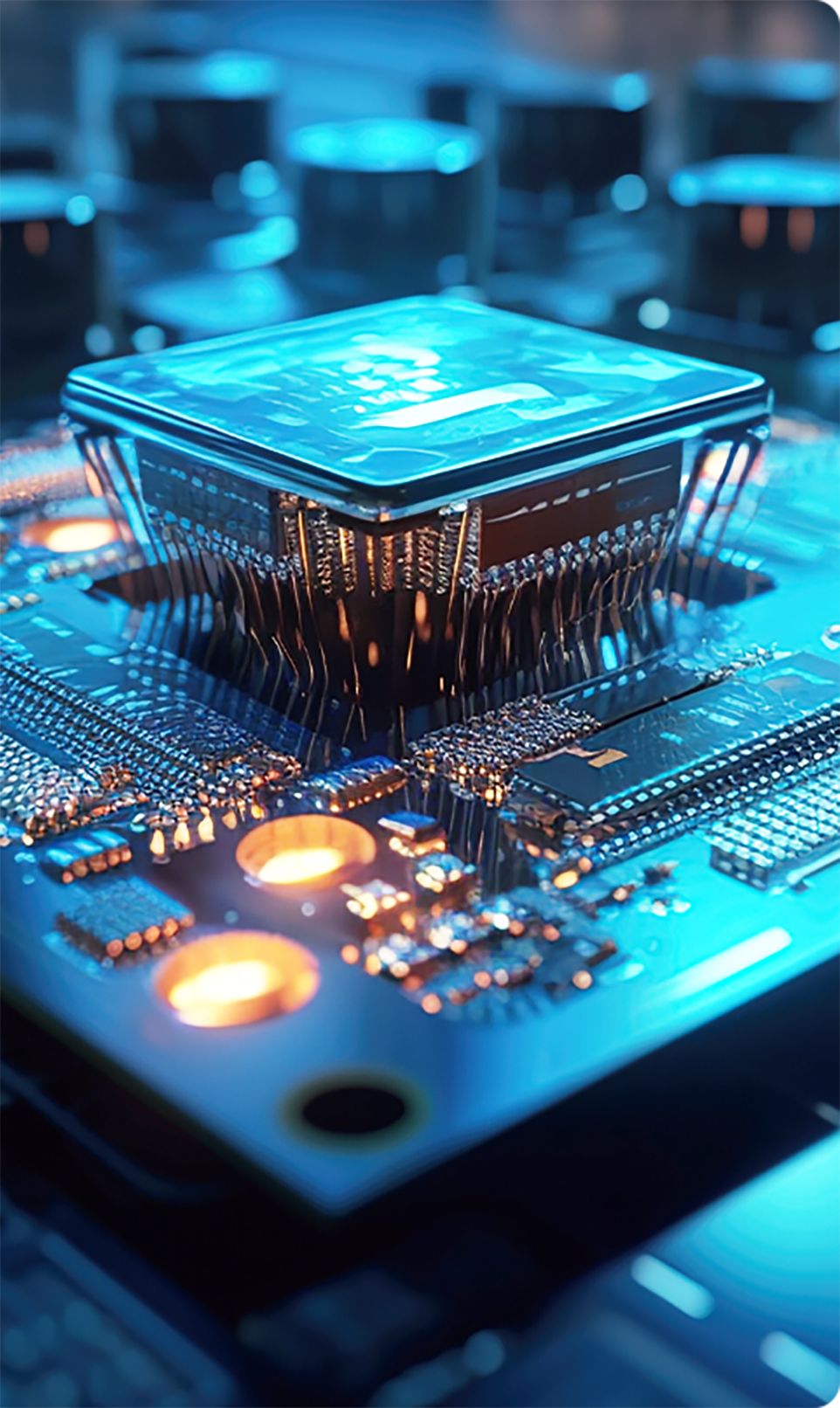

产品

MCU

逻辑芯片

交叉检索

咨询热线